#### THÈSE

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité Informatique

Arrêté ministériel: 7 août 2006

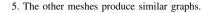

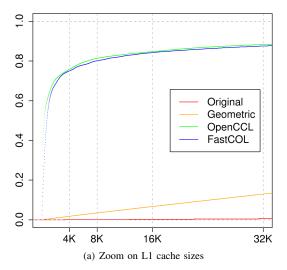

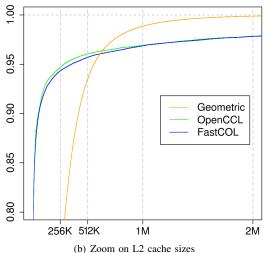

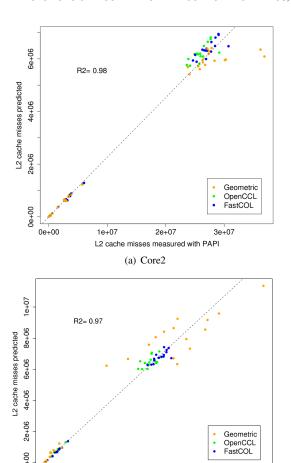

Présentée et soutenue publiquement par

Marc Tchiboukdjian

le 9 décembre 2010

### Algorithmes parallèles efficaces en cache Applications à la visualisation scientifique

Thèse dirigée par Denis Trystram et codirigée par Vincent Danjean, Jean-Philippe Nominé et Bruno Raffin

#### **JURY**

| M. Christoph Dürr           | DR CNRS                        | Président   |

|-----------------------------|--------------------------------|-------------|

| M. Jean-Michel DISCHLER     | Prof. Université de Strasbourg | Rapporteur  |

| M. Enrique S. Quintana Ortì | Prof. Universidad Jaime I      | Rapporteur  |

| M. Vincent Danjean          | MdC Université Joseph Fourier  | Examinateur |

| M. Jean-Philippe Nоміné     | Chercheur CEA,DAM,DIF          | Examinateur |

| M. Bruno Raffin             | CR INRIA                       | Examinateur |

| M. Denis Trystram           | Prof. Grenoble INP             | Examinateur |

| M. Frédéric VIVIEN          | DR INRIA                       | Examinateur |

Thèse préparée au sein du Laboratoire d'Informatique de Grenoble dans l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

## Sommaire

| Sc                        | ommaire                                                                                                                                   | iii               |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| In                        | troduction                                                                                                                                | 1                 |

| Ι                         | État de l'art                                                                                                                             | 13                |

| 1                         | Applications limitées par les accès mémoire                                                                                               | 15                |

| 2                         | Algorithmes utilisant efficacement les caches                                                                                             | 25                |

| 3                         | Programmation parallèle par vol de travail                                                                                                | 39                |

| 4                         | Algorithmes parallèles efficaces en cache                                                                                                 | 61                |

| II                        | Contributions                                                                                                                             | <b>75</b>         |

| 5                         | Maillage cache-oblivious pour la visualisation scientifique<br>Binary Mesh Partitioning for Cache-Efficient Visualization                 | <b>77</b><br>81   |

| 6                         | Extraction d'isosurfaces parallèle et efficace en cache<br>Cache-Efficient Parallel Isosurface Extraction for Shared Cache Multicores .   | <b>95</b><br>103  |

| 7                         | Vol de travail efficace en cache pour les boucles parallèles<br>A Work Stealing Scheduler for Parallel Loops on Shared Cache Multicores . | <b>113</b><br>119 |

| 8                         | Nouvelle analyse des ordonnancements par vol de travail Decentralized List Scheduling                                                     | <b>129</b><br>133 |

| C                         | onclusion                                                                                                                                 | 155               |

| Bi                        | ibliographie                                                                                                                              | 159               |

| Ta                        | able des figures                                                                                                                          | 169               |

| Ta                        | able des matières                                                                                                                         | 171               |

| $\mathbf{R}_{\mathbf{c}}$ | ésumés                                                                                                                                    | 177               |

#### Introduction

Le classement du Top500 <sup>1</sup> reporte deux fois par an les performances atteintes par les 500 calculateurs les plus puissants au monde sur une application de référence, le LINPACK [DLP03]. Lors du dernier classement en juin 2010, la machine la plus puissante a atteint la vitesse de 1,759 petaflops <sup>2</sup> à l'aide de 224162 cœurs. Les performances de la meilleure machine sont multipliées par environ 1000 tous les 10 ans ce qui permet de prévoir que la puissance d'un exaflops sera vraisemblablement atteinte dès 2018.

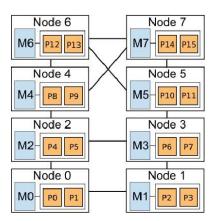

Un exemple de supercalculateur est la machine TERA-100 du CEA DAM qui s'architecture comme suit. La brique de base est le nœud de calcul composé de 4 processeurs octocœurs Intel Nehalem EX à 2.27 Ghz. Ces nœuds sont ensuite regroupés par paquets de 324 en un "ilôt" et connectés par un switch de bande passante 51.8 Tbps. Les 14 ilôts communiquent entre eux par l'intermédiare de 27 switch de 36 ports chacun ayant une bande passante de 2.88 Tbps. Au total, la machine TERA-100 contient 138000 cœurs donnant une puissante théorique crête de 1,25 pétaflops, 291 To de mémoire, consomme mois de 6 MW et occupe 750m².

Dans une telle machine, on peut distinguer deux niveaux suivant le mode de communication entre les cœurs. Tous les cœurs à l'échelle d'un nœud accèdent la même mémoire et peuvent donc partager des données et coopérer très rapidement par des lectures et écritures en mémoire. A l'échelle de l'ilôt, les cœurs communiquent par messages sur le réseau et les données doivent être distribuées sur les différentes zones de mémoire.

Exploiter efficacement la puissance d'une telle machine soulève principalement deux défis :

- 1. le parallélisme : répartir de manière équilibrée les calculs sur plus de 100000 cœurs,

- 2. la hiérarchie mémoire : la vitesse des accès mémoire et des communications est fonction de la distance.

Pour réduire les temps de communications entre les cœurs et la latence des accès à la mémoire, la structure d'une application doit reflèter la hiérarchie de l'organisation de la machine. Les parties de code séquentielles sont optimisées pour tirer parti des différents niveaux de caches. L'exécution parallèle profite du cache partagé à l'échelle d'un processeur et de la mémoire partagée à l'échelle d'un nœud. Les cœurs ne communiquent par le réseau que pour sortir d'un nœud et on essaye de réduire les communications à l'échelle de la machine au profit des communications à l'échelle de l'ilôt.

Lorsque le comportement de l'application est statique et connu avant l'exécution, il est déjà difficile pour le programmeur de concevoir et d'optimiser le code à tous ces niveaux. De plus, du bruit inhérent à la taille d'une telle machine vient compromettre l'équilibre parfait prévu et espéré par le programmeur [Sni09]. Enfin, si le comportement

<sup>1.</sup> http://www.top500.org

<sup>2.</sup> Un petaflop correspond à  $10^{15}$  opérations flottantes par seconde

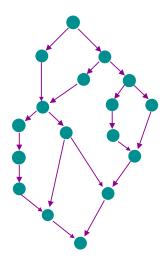

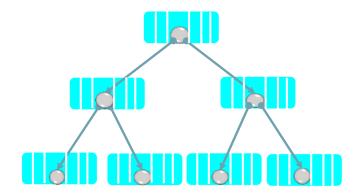

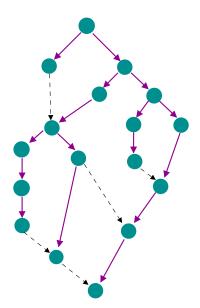

FIGURE 1 – Programme parallèle à base de tâches. L'exécution des tâches doit respecter les contraintes de précédence.

même de l'application devient dynamique, il est extrèmement complexe d'adapter la décomposition de l'application pour garder un bon équilibrage de charge et une bonne localité des accès mémoire et des communications.

Idéalement, on aimerait pouvoir cacher cette complexité au programmeur à travers une interface de programmation simple mais donnant suffisament d'informations sur le comportement de l'application. Un moteur d'exécution s'occupe alors de décomposer l'application en fonction de l'architecture de la machine et gère la répartition de charge et les communications en optimisant la localité. On fournit au programmeur un modèle de machine abstraite exprimant les contraintes du parallélisme et de la localité pour guider ses choix lors de la conception. Si l'application respecte les contraintes de performances du modèle, elle s'exécute alors aussi efficacement qu'une application spécifiquement conçue et optimisée pour la machine cible. Les avantages d'une telle approche sont un code plus simple et des applications portables qui peuvent s'adapter à un comportement dynamique (du matériel ou de l'application).

A l'heure actuelle, il est difficile d'envisager une telle interface et son moteur associé qui soit capable de s'exécuter efficacement à l'échelle de la machine entière. La programmation pour mémoire distribuée nécessite la description des données dans l'interface et on ne dispose pas de modèles généraux et efficaces. De plus, une décomposition de l'application résultant en une localité non optimale est très coûteuse à cause de la lenteur des communications sur le réseau. Les approches actuelles ont une efficacité qui est limitée à des cas particuliers : peu de transferts de données [GRCD98] ou applications très régulières [GBH+06].

Pour la programmation parallèle en mémoire partagée, il n'est pas nécessaire de décrire les données et de gérer les communications. L'interface est donc plus simple. On doit quand même gérer les accès à la mémoire mais ils sont moins coûteux que les communications donc un comportement non optimal n'empèche pas d'obtenir de bonnes performances.

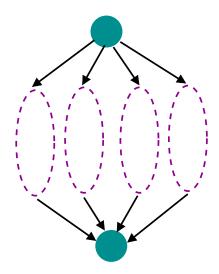

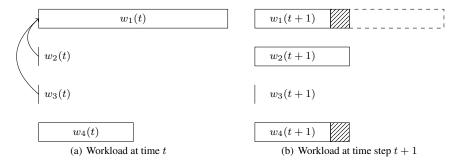

Une interface simple pour décrire le parallélisme d'une application est la programmation à base de tâches (cf. figure 1). L'application crée des tâches qui décomposent

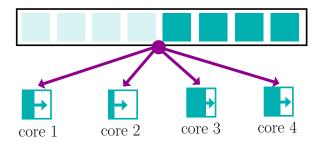

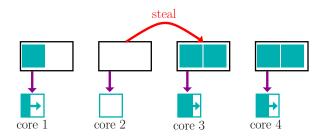

FIGURE 2 – Ordonnancement par liste centralisée. La contention lors de l'accès à la liste limite le passage à l'échelle.

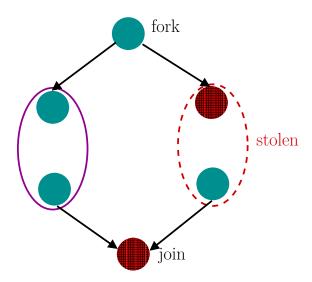

FIGURE 3 – Ordonnancement par vol de travail. La liste est décentralisée et cela réduit fortement la contention.

le calcul en petites parties séquentielles. Elle déclare aussi des précédences entre ces tâches pour déterminer à partir de quand une tâche peut être exécutée, par exemple si cette tâche dépend du résultat d'autres tâches. Le moteur exécutif est responsable de l'ordonnancement de ces tâches. Il décide à quel moment et sur quel cœur exécuter chaque tâche. Pour une exécution efficace, le moteur doit trouver un ordonnancement qui minimise le temps de complétion de l'application. De plus, le coût de calcul de cet ordonnancement doit être faible afin de laisser le plus de ressources possibles à l'application.

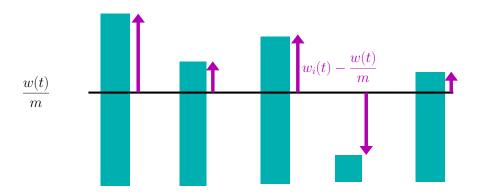

Un ordonnancement efficace et rapide à obtenir est donné par l'algorithme de liste de Graham [Gra69]. Toutes les tâches prêtes, c'est-à-dire dont les précédences sont satisfaites, sont stockées dans une liste (cf. figure 2). Dès qu'un cœur est inactif, il retire une tâche de cette liste et l'exécute. Les nouvelles tâches générées sont ajoutées à la liste. L'ordonnancement généré par cet algorithme est proche de l'optimal. Si on note W le travail total de toutes les tâches et D le travail des tâches sur un plus long chemin de précédences, le temps d'exécution  $T_m$  de l'application sur m cœurs est majoré par

$$T_m \le \frac{W}{m} + \left(1 - \frac{1}{m}\right) \cdot D. \tag{1}$$

Les deux termes de cette équation, W/m et D, sont des bornes inférieures du temps d'exécution. Cet ordonnancement est donc au plus à un facteur 2 de l'optimal. Cependant, l'implémentation d'une telle liste de tâches n'est pas efficace en pratique. En effet, cette liste est centralisée ce qui provoque de la contention lors de son accès en concurrence par de nombreux cœurs.

La technique clé qui permet de construire un moteur d'exécution efficace pour les programmes parallèles à base de tâches est le vol de travail [BL99]. A la place d'une liste de tâches centralisée, chaque cœur maintient ses tâches à exécuter dans une liste

locale (cf. figure 3). Lorsque qu'une liste devient vide, un cœur tente de voler des tâches dans la liste d'un autre cœur sélectionné au hasard. Comme les opérations de vol de tâches, c'est-à-dire l'accès à une liste distante, sont peu fréquentes, il y a peu de chance que deux cœurs accèdent à la même liste au même moment ce qui réduit fortement la contention. De plus, le vol de travail génère un ordonnancement aussi bon que l'algorithme de liste de Graham. Blumofe et al. [BL99, ABP98] ont montré que le temps d'exécution était borné par

$$T_m \le \frac{W}{m} + O(D) \tag{2}$$

en prenant en compte le coût du calcul de l'ordonnancement.

L'équation (2) permet de guider le programmeur lors de la conception d'un algorithme parallèle. L'algorithme parallèle doit à la fois minimiser le travail, c'est-à-dire le nombre de calculs à effectuer W, mais aussi minimiser la profondeur D du calcul, c'est-à-dire le nombre maximal d'instructions sur un chemin de précédences. On définit le parallélisme de l'algorithme comme le rapport du travail sur la profondeur W/D. Si le parallélisme est très supérieur au nombre de processeurs, c'est-à-dire  $W/D \gg m$ , alors l'exécution de l'application avec un moteur de vol de travail sera très efficace. En effet, la borne sur le temps d'exécution donnée par l'équation (2) devient

$$T_m \le (1 + o(1)) \cdot \frac{W}{m}.\tag{3}$$

Le surcoût par rapport à une décomposition parfaite et statique du travail W/m est donc très faible. De plus, dans le cas du programme parallèle par tâches, cette décomposition n'est pas fonction de l'architecture de la machine (nombre et vitesses des cœurs). L'application est donc portable et peut s'adapter à un comportement dynamique. On qualifie de processor-aware un programme parallèle dont la décomposition est fonction du nombre de cœurs. Lorsque la décomposition du calcul n'est pas fonction du nombre de cœurs, comme pour le programme par tâches, le programme est dit processor-oblivious. Un moteur à base de vol de travail permet d'exécuter un programme processor-oblivious exposant beaucoup de parallélisme aussi efficacement qu'un programme processor-aware.

L'interface de programmation parallèle par tâches associée à un ordonnancement par vol de travail s'est imposée comme le standard pour la programmation efficace en mémoire partagée. Une des premières implémentations est le logiciel Cilk du MIT [BJK<sup>+</sup>96] en 1994. Cette technique a été reprise dans les logiciels TBB de Intel [KV07], Cilk++ startup du MIT rachetée par Intel, TPL de Microsoft [LSB09], etc. La programmation par tâches a fait son apparition dans le standard OpenMP [Ope] à partir de la version 3.

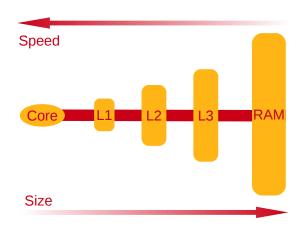

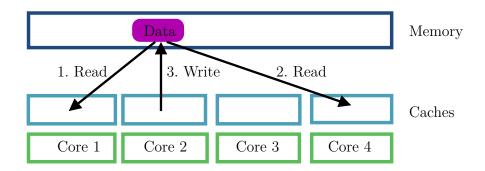

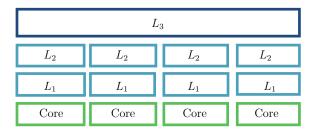

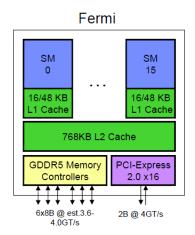

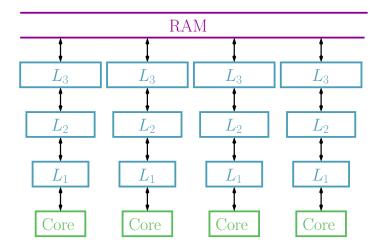

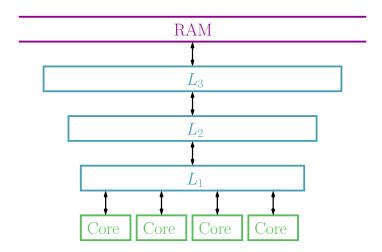

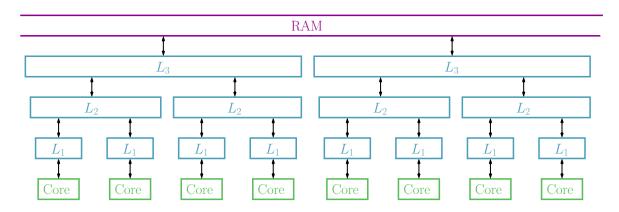

Le deuxième défi à relever pour exploiter efficacement les performances des supercalculateurs est la prise en compte de la hiérarchie mémoire. Pour réduire la latence des accès à la mémoire, les processeurs contiennent plusieurs niveaux de caches entre les cœurs et la mémoire centrale (cf. figure 4). Chaque niveau de cache est plus rapide que le précédent mais a une capacité plus faible. Les données transitent entre ces caches par blocs contigus appelés lignes de cache. Les processeurs de la machine TERA-100 ont 3 niveaux de cache de tailles 32KO, 256KO et 24MO et des lignes de cache de 64O.

FIGURE 4 – Hiérarchie mémoire composée de 3 niveaux de cache et de la mémoire centrale.

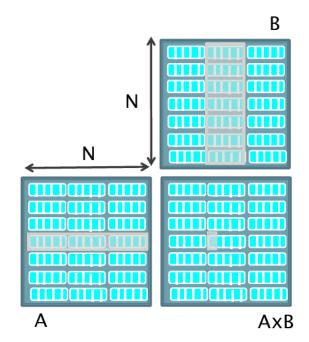

FIGURE 5 – Trois schémas d'accès. Le schéma de gauche n'est pas local. Le schéma du milieu est *cache-aware*, c'est-à-dire optimisé pour une taille de cache précise. Le schéma de droite est *cache-oblivious*, c'est-à-dire optimisé pour toutes les tailles de cache.

Pour tirer parti de ses caches, les accès mémoire de l'application doivent être locaux : réutiliser la même donnée ou une donnée proche dans la mémoire dans un court laps de temps.

Pour améliorer la localité des accès mémoire d'une application, on peut décomposer le calcul de la façon suivante (cf. figure 5):

- 1. charger un bloc de données correspondant à la taille du cache,

- 2. exécuter tous les calculs utilisant ces données.

Lorsqu'il y a plusieurs niveaux de cache, on décompose le calcul de façon hiérarchique : on charge un bloc de données correspondant à la taille du plus gros cache, puis un bloc de données correspondant à la taille du niveau inférieur, etc. Cette technique est utilisée, par exemple, dans l'implémentation des BLAS pour les calculs d'algèbre linéaire sur les matrices denses [WP05]. On qualifie les algorithmes utilisant cette technique d'algorithmes cache-aware [AV88] car ils utilisent la taille des caches. Les inconvénients de cette approche cache-aware sont identiques à ceux de l'approche processor-aware : le code devient complexe dès qu'il y a plusieurs niveaux de cache, l'application n'est pas portable et ne peut pas s'adapter à une variation des paramètres (e.g. réduction de la taille du cache due à la présence d'une autre application ou pour économiser de l'énergie). Une difficulté supplémentaire à laquelle les programmeurs doivent faire face

dans le cas des algorithmes *cache-aware* réside dans la taille des blocs de données : la taille optimale ne correspond pas toujours à la taille du cache. Il est nécessaire de recourir à l'expérimentation pour trouver la taille de blocs optimale [WP05].

Pour pallier les inconvénients de l'approche aware, on peut utiliser une approche similaire à celle utilisée pour le parallélisme. L'approche est beaucoup plus simple pour les caches car ils sont gérés de manière transparente par le matériel. Ce sont des fonctions internes au processeur qui décident quelles données charger dans quel cache. Les données répondent aux accès mémoire de façon transparente qu'elles soient en cache ou non. L'étape numéro 1 de la technique cache-aware, charger un bloc de données dans le cache, n'est pas réalisée par l'application mais par le matériel. On n'a donc pas besoin ici d'une interface ni de moteur d'exécution.

De la même façon que la programmation par tâches décompose le calcul au grain le plus fin sous forme de tâches pour pouvoir s'exécuter efficacement quel que soit le nombre de processeurs, on peut décomposer les accès mémoire au grain le plus fin pour obtenir une bonne localité à toutes les échelles (cf. figure 5). Un exemple de technique qui permet de s'affranchir de la taille des caches dans la décomposition du calcul par blocs est de découper le calcul en blocs de taille moitié récursivement. De tels algorithmes qui n'utilisent pas les paramètres des caches sont qualifiées de cache-oblivious [FLPR99].

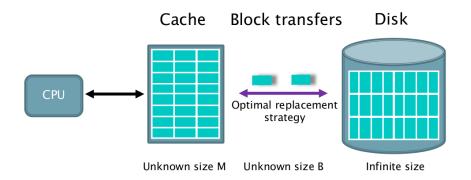

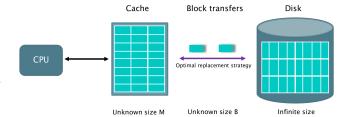

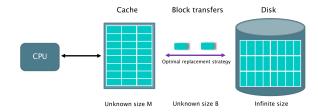

Le modèle cache-oblivious permet de guider le programmeur lors de la conception d'un algorithme. Ce modèle est composé de deux niveaux de mémoire, un niveau rapide mais de capacité limitée M et un niveau lent de capacité infinie. Les données sont transférées entre ces deux niveaux par blocs contigus de taille B. Une particularité intéressante de ce modèle est d'interdire à l'algorithme d'utiliser ces paramètres M et B. Sous certaines conditions de régularité des accès mémoire, on peut montrer qu'un algorithme optimal dans le modèle cache-oblivious est optimal à tous les niveaux de la hiérarchie mémoire quelque soient le nombre de niveaux et la taille des caches.

Un avantage supplémentaire des techniques *cache-oblivious* apparait lors de l'utilisation de nœuds de calculs hybrides contenant des processeurs classiques et des processeurs graphiques (GPU). Une structure de donnée optimisée dans le modèle *cache-oblivious* peut être partagée par ces deux types de processeurs ayant des hiérarchies de cache très différentes sans avoir besoin de l'optimiser pour chacun des processeurs séparemment.

Cependant, il n'est pas toujours possible d'obtenir un algorithme *cache-oblivious* aussi performant qu'un algorithme *cache-aware*, soit pour des raisons d'impossibilité théorique soit parce que les algorithmes *cache-oblivious* connus ne sont pas efficaces en pratique, souvent à cause d'un surcoût en nombre d'instructions.

Les techniques *oblivious* pour la hiérarchie mémoire et pour le parallélisme permettent de limiter l'impact de la complexité de l'architecture sur le code de l'application. De plus, les applications obtenues sont portables et peuvent s'adaptater a une variation des paramètres de l'architecture.

Pour développer des applications parallèles et efficaces en cache, nous proposons de combiner les approches *processor-oblivious* et *cache-oblivious*.

Deux difficultés majeures rendent ce couplage non trivial. La hiérarchie mémoire est plus complexe en parallèle qu'en séquentiel. En effet, en parallèle, plusieurs niveaux de caches séparent les cœurs de la mémoire et ces niveaux peuvent être :

- privés : chaque cœur possède son propre cache, ou

- partagés : plusieurs cœur partagent un même cache.

FIGURE 6 – Le contenu d'un cache privé n'est pas indépendant des actions des autres cœurs. Ici le cœur 2 modifie des données qui ont été préalablement chargées dans les caches des cœurs 1 et 4. Pour garder les caches et la mémoire en cohérence, les données des cœurs 1 et 4 sont invalidées. Une lecture de la même donnée par le cœur 1 nécessitera un accès à la mémoire et non pas au cache pour obtenir une version à jour.

FIGURE 7 – Influence de l'ordonnancement sur l'utilisation du cache. L'ordonnancement de droite est plus efficace que l'ordonnancement de gauche car les tâches utilisant des données communes sont exécutées sur des cœurs partageant le même cache. Images de [Dre07].

Il faut donc adapter le comportement de l'algorithme en fonction du type de cache. De plus, l'état du cache d'un cœur n'est pas indépendant du comportement des autres cœurs, même dans le cas des caches privés à cause du protocole de cohérence de cache (voir la figure 6).

Il faut adapter l'algorithme mais aussi l'ordonnanceur car la politique d'ordonnancement des tâches a un fort impact sur le comportement du cache (voir la figure 7). En particulier les stratégies de vol qui sont efficaces pour minimiser le coût de l'ordonnanceur ne sont pas les mêmes que les stratégies qui maximisent l'utilisation des caches, surtout pour les caches partagés. Une politique d'ordonnancement efficace s'efforcera de ne pas perturber les caches privés tout en garantissant un usage coopératif des caches partagés.

Afin de vérifier expérimentalement l'efficacité des politiques d'ordonnancement que nous proposons dans cette thèse, nous avons utilisé ces techniques pour optimiser plusieurs applications du domaine de la visualisation scientifique. Les applications de visualisation scientifique traitent de grosses masses de données et sont donc gourmandes à la fois en accès mémoire et en puissance de calculs. Mieux tirer parti du parallélisme et de la hiérarchie mémoire permet donc d'améliorer les performances de ces applications.

La simulation numérique consiste à calculer par ordinateur l'évolution d'un système physique complexe dont on connait un modèle théorique mais qui est difficile ou impossible à résoudre analytiquement. Elle prend une importance grandissante dans de

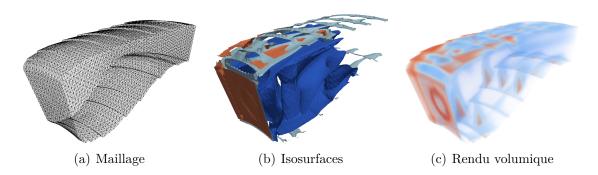

FIGURE 8 – Simulation de la densité d'essence au sein d'une chambre de combustion. De gauche à droite, le maillage, une représentation graphique de la densité d'essence avec 3 isosurfaces et avec un rendu volumique. (maillage de VTK, courtoisie de W. J. Schroeder).

nombreux domaines scientifiques ainsi que dans l'industrie. Un exemple intéressant de simulation numérique à grande échelle est la simulation de l'univers depuis le big bang par le projet Horizon<sup>3</sup>. Cette simulation a durée deux mois sur les 6144 processeurs d'un supercalculateur du centre de calcul du CEA (CCRT) et a généré 50To de données.

La visualisation scientifique fournit sous une forme graphique les résultats de la simulation et aide ainsi à la compréhension du phénomène simulé. C'est aujourd'hui un outil indispensable pour analyser les grandes quantités de données produites par ces simulations. Pour répondre aux utilisateurs en attente d'une interaction fluide lors de l'analyse de ces données, il faut des algorithmes performants adaptés aux architectures des processeurs modernes.

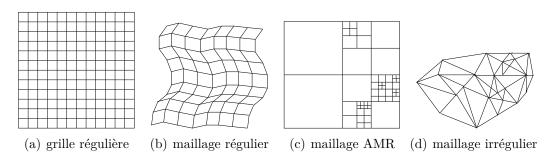

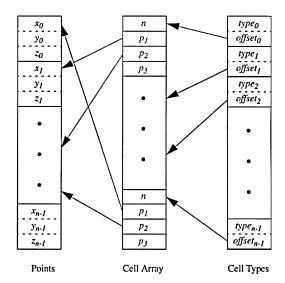

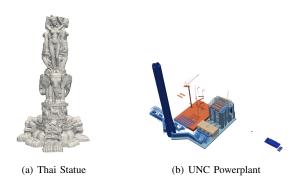

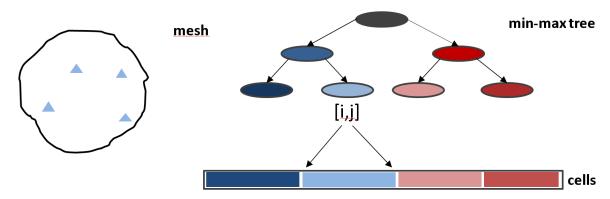

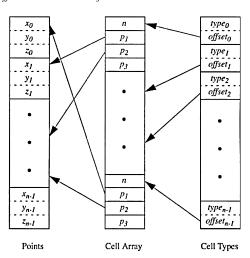

Une représentation graphique de données scientifiques s'obtient généralement en appliquant un ou plusieurs filtres sur un maillage [HJ04]. Un maillage est une représentation discrète pour stocker une fonction de l'espace tridimensionnel ou champ (voir la figure 8(a)). L'espace est divisé en unités élémentaires appelée cellules (e.g. tétraèdres, hexaèdres, etc.), chaque cellule étant définie par une liste de points. Chaque point du maillage a une position dans l'espace ainsi que la valeur du champ en ce point. La valeur de la fonction dans le reste de l'espace du maillage est reconstruite par interpolation linéaire à l'intérieur de chaque cellule.

Les filtres de visualisation de champs scalaires 3D les plus classiques sont l'extraction d'isosurfaces (voir la figure 8(b)) et le rendu volumique (voir la figure 8(c)). Une isosurface est l'ensemble des points de l'espace ayant la même valeur de champ. Une isosurface est habituellement représentée par une surface triangularisée.

Pour générer un rendu volumique, on associe à chaque valeur du champ scalaire une couleur et une opacité par l'intermédiaire de fonctions de transfert. La couleur d'un pixel de l'image finale correspond à l'accumulation des valeurs de couleur atténuée par les valeurs d'opacité sur la trajectoire d'un rayon lancé à partir du point de vue et passant par le centre du pixel.

<sup>3.</sup> http://www.projet-horizon.fr

#### Contributions

Nos contributions s'articulent principalement autour de deux points.

- Nous appliquons tout d'abord les techniques *cache-oblivious* pour améliorer la localité mémoire des filtres de visualisation scientifique.

- Nous montrons ensuite comment modifier l'ordonnancement de tels filtres pour que l'exécution parallèle conserve la localité de l'exécution séquentielle.

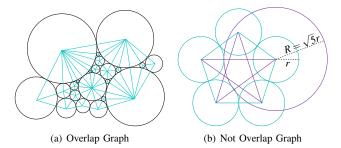

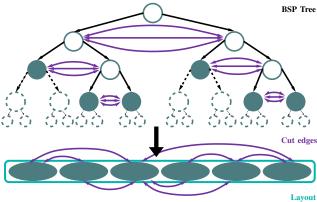

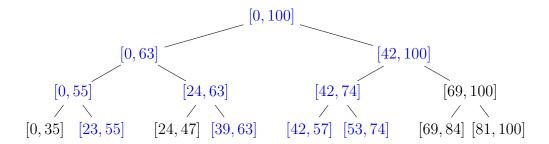

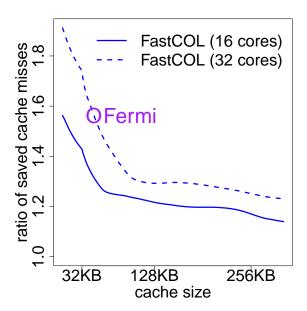

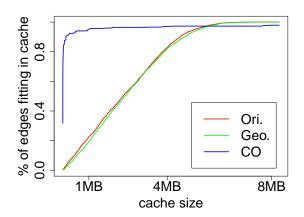

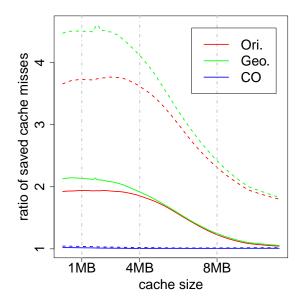

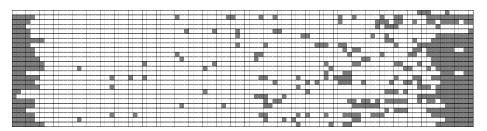

Afin d'améliorer la localité des filtres de visualisation, nous proposons de réorganiser la structure de données représentant le maillage. En effet, c'est sur cette structure que se concentrent la majorité des accès mémoire. Il existe deux grandes familles de maillages : les maillages réguliers et les maillages irréguliers. La structure de données représentant les maillages réguliers est similaire à celle des matrices denses. Les techniques cache-oblivious utilisées pour l'optimisation des calculs d'algèbre linéaire dense (e.q. les space-filling curves) s'adaptent parfaitement aux maillages réguliers [PF01] Le cas des maillages irréguliers est plus difficile. Yoon et al. proposent dans [YLPM05] un algorithme de réorganisation de maillages irréguliers appelé OpenCCL. Cet algorithme donne de bons résultas expérimentaux mais sans garantie théorique. Nous proposons une alternative appelée FastCOL qui permet d'obtenir un niveau de performance équivalent mais avec une garantie théorique. Cette organisation est obtenue par une découpe récursive du maillage sous forme d'arbre de BSP (Binary Space Partitioning) utilisant le séparateur de Miller et al. [MTTV98]. Nous donnons une garantie théorique sur le nombre de défauts de cache générés dans le cas de schémas d'accès classiques. Lorsque le schéma d'accès du filtre respecte la localité définie par les relations de voisinage du maillage, nous montrons que le nombre de défauts de cache sur un maillage de taille S est borné par

$$\frac{S}{B} + O\left(\frac{S}{M^{1/3}}\right)$$

avec B la taille des lignes de cache et M la taille du cache. Le premier terme représente le nombre de défauts de cache nécessaire pour lire entièrement le maillage avec une localité spatiale parfaite. Le deuxième terme est le surcoût induit par la découpe des cellules lors de l'utilisation du séparateur. Cette garantie est valable quel que soit la valeur de ces paramètres et est donc cache-oblivious. Des expérimentations sur de nombreux filtres de visualisation usuels confirment des gains de performance significatifs sur CPU et sur GPU.

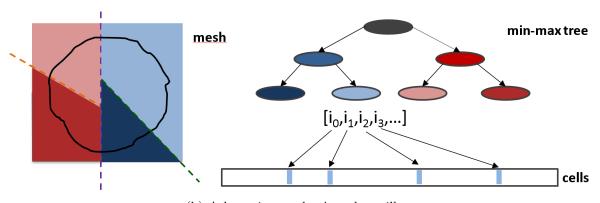

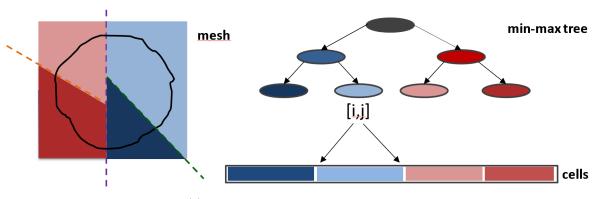

Certains filtres de visualisation utilisent également une structure d'arbre pour accélérer les traitements sur le maillage. Nous montrons qu'il est possible d'améliorer la localité de tels filtres en utilisant la même structure que l'arbre de BSP calculé lors de la réorganisation. Le schéma d'accès de ces filtres est alors adapté au maillage généré par FastCOL ce qui améliore la localité. Nous appliquons cette technique à l'arbre min-max qui permet d'accélérer l'extraction d'isosurfaces. Des expériences montrent le gain de performance par rapport à l'utilisatoin d'un arbre géométrique standard (e.g. kd-tree ou BSP tree). Cette technique permet en outre, dans le cas particulier de l'arbre min-max, de réduire la consommation mémoire.

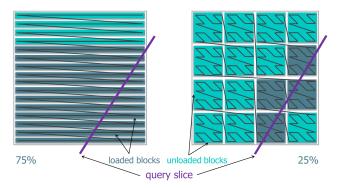

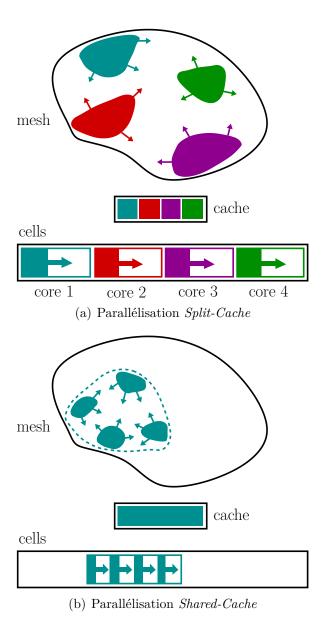

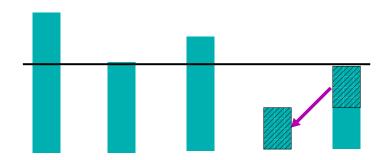

Nous montrons ensuite comment conserver la localité des accès mémoire lors d'une exécution parallèle. Nous étudions le cas particulier des boucles parallèles où chaque itération peut être traitée indépendamment. Ce schéma parallèle est très courant, particulièrement dans les filtres de visualisation scientifique qui appliquent souvent

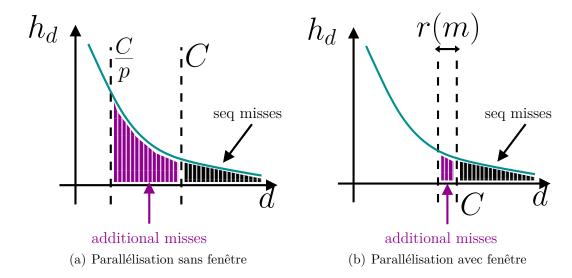

une même opération à chaque élément du maillage. Les ordonnancements par vol de travail permettent de paralléliser les boucles avec très peu de surcoût par rapport à une implémentation statique processor-aware. Cependant, nous montrons que de tels ordonnancements génèrent plus de défauts de cache que l'exécution séquentielle sur un cache partagé. Si l'exécution séquentielle cause  $Q_{\rm seq}(M)$  défauts de cache sur un cache de taille M, l'exécution parallèle standard sur p cœurs partageant un cache de taille M cause autant de défauts de cache que l'exécution séquentielle sur un cache de taille M/p:

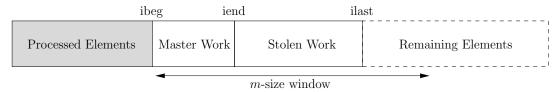

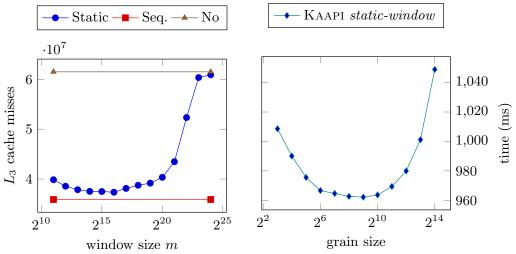

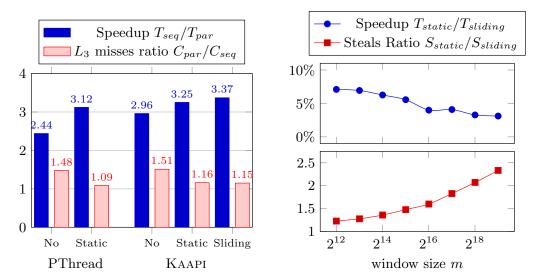

$$Q_{\text{par}}(M) = Q_{\text{seq}}\left(\frac{M}{p}\right).$$

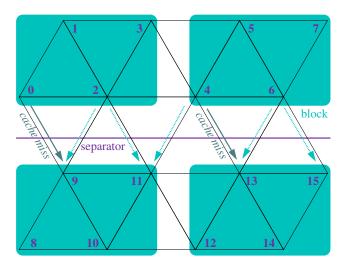

En effet, les cœurs travaillent sur des données très éloignées en mémoire et sont donc en compétition pour l'utilisation du cache. Ils n'obtiennent chacun qu'une fraction M/p du cache partagé. Pour favoriser l'usage coopératif du cache partagé, nous proposons un nouvel ordonnancement des boucles parallèles par vol de travail qui incite les cœurs à accéder à des données proches en mémoire de celles déjà chargées dans ce cache partagé. Cet ordonnancement est basé sur une fenêtre de la taille du cache partagé glissant sur les données. Une modification de l'algorithme de vol contraint tous les cœurs à travailler sur des données à l'intérieur de la fenêtre et donc dans le cache. Nous montrons qu'une telle exécution n'induit q'une augmentation légère des défauts de cache par rapport à l'exécution séquentielle. Des expériences sur les filtres d'extraction d'isosurfaces confirment l'analyse théorique. De plus, l'implémentation de l'ordonnancement avec fenêtre est très efficace et ne génère que peu de surcoût par rapport à l'implémentation sans fenêtre.

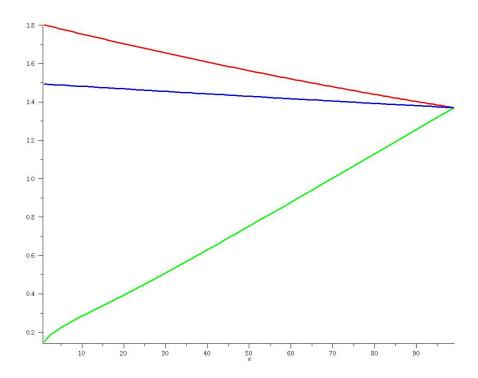

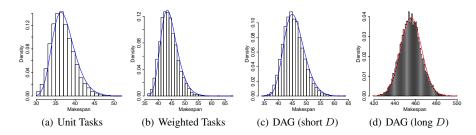

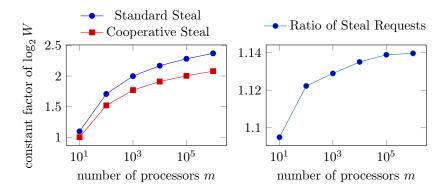

Enfin ce travail nous a conduit à développer une nouvelle analyse théorique du vol de travail qui vise à mieux comprendre le nombre de vols S lors d'une exécution par vol de travail. En effet, l'analyse de Blumofe  $et\ al.\ [ABP98]$  ne donne qu'une borne très large sur le nombre de vols avec un facteur constant important,  $S=O(m\cdot D)$  avec m le nombre de cœurs et D la profondeur du graphe de précédences. De plus, cette analyse ne s'applique qu'à une classe restreinte de graphes de précédences ne comprenant pas directement les boucles parallèles. Notre analyse caractérise précisément le nombre de vols S. Des simulations montrent que la constante obtenue est à moins de 40% de la valeur théorique. En outre, elle ne se base pas sur la profondeur du graphe mais sur l'équilibrage de charge au moment du vol. Elle peut donc s'appliquer directement au cas des boucles parallèles et permet également d'évaluer l'efficacité de nouveaux mécanismes de vols (comme la combinaison des requêtes de vols).

#### Contexte

J'ai étudié les algorithmes *cache-oblivious* lors d'un master réalisé à l'université de Stony Brook aux États-Unis sous l'encadrement du professeur Michael Bender, spécialiste en ordonnancement et en algorithmique.

Les applications en visualisation scientifique sont le fruit d'une collaboration avec l'équipe de visualisation scientifique du département des sciences de la simulation et de l'information du CEA de Bruyères-Le-Chatel. C'est Jean Philippe Nominé qui m'a encadré sur les problématiques de visualisation de grosses masses de données au CEA.

La plupart de ce travail s'est déroulé dans l'équipe projet MOAIS <sup>4</sup> qui fait partie de l'INRIA et du laboratoire d'informatique de Grenoble <sup>5</sup>. Les thèmes de recherches de l'équipe en relation avec cette thèse sont l'ordonnancement, l'algorithmique et la programmation parallèle. En plus de l'encadrement de Vincent Danjean et Bruno Raffin sur toutes ces thématiques ainsi que sur la visualisation scientifique, j'ai travaillé en collaboration avec :

- Thierry Gautier et Fabien Le Mentec sur les aspects de performances en pratique du vol de travail et en particulier sur le moteur exécutif de vol de travail X-KAAPI,

- Nicolas Gast, Jean-Louis Roch, Denis Trystram et Frédéric Wagner sur l'analyse théorique du vol de travail.

Pendant cette thèse, j'ai aussi eu l'occasion d'encadrer et de travailler avec plusieurs stagiaires :

- Bruno Berthier sur les arbres min-max pour l'extraction d'isosurface,

- Siméon Marijon sur les organisations mémoire de maillage spécifiques aux GPU,

- Aymerick Chincolla, Adrien Graton et Matthieu Westphal sur le rendu volumique par lancer de rayons,

- Thibault Bruguet sur les algorithmes parallèles pour cache partagé.

#### Organisation du manuscrit

Le manuscrit est composé de deux parties. La première partie intitulée "État de l'art" invoque les notions générales et les résultats connus à travers les 4 premiers chapitres. Dans le chapitre 1, nous étudions l'impact des accès mémoire sur le temps d'exécution d'une application et les techniques pour réduire le temps d'accès à la mémoire. Dans le chapitre 2, nous passons en revue les modèles cache-aware et cache-oblivious. Dans le chapitre 3, nous présentons la programmation parallèle à base de tâches et l'ordonnancement par vol de travail. Dans le chapitre 4, nous analysons les différents impacts du parallélisme sur les caches. Nous présentons les résultats existants sur l'ordonnancement et les algorithmes parallèles pour les caches privés et les caches partagés.

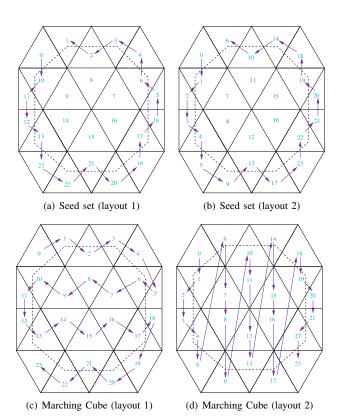

La deuxième partie intitulée "Contributions" est constituée des 4 publications réalisées dans le cadre de cette thèse. Dans l'article Binary Mesh Partitioning for Cache-Efficient Visualization [TDR10a], nous présentons notre nouvelle organisation mémoire cache-oblivious FastCOL. Dans l'article Cache-Efficient Parallel Isosurface Extraction for Shared Cache Multicores [TDR10b], nous étudions le cas particulier de l'extraction d'isosurface. Nous montrons comment adapter l'arbre min-max au maillage FastCOL et proposons un schéma de parallélisation processor-aware qui ne génère pas plus de défauts de cache que l'exécution séquentielle. Dans l'article A Work Stealing Scheduler for Parallel Loops on Shared Cache Multicores [TDG+10], nous rendons processor-oblivious le schéma proposé dans l'article précédent en utilisant du vol de travail. Nous montrons également que cet ordonnancement garantit un nombre de défauts de cache équivalent à l'exécution séquentielle dans le cas général et non pas uniquement dans le cadre des filtres de visualisation basé sur le maillage FastCOL. Dans l'article A Tighter Analysis of Work Stealing [TGT+10], nous donnons une nouvelle analyse plus précise

<sup>4.</sup> http://moais.imag.fr

<sup>5.</sup> http://www.liglab.fr

du vol de travail qui permet d'étudier des modifications fines de l'ordonnanceur.

Nous terminons ce manuscrit par un bilan des travaux effectués et une suggestion des pistes qui sont, à notre avis, les plus intéressantes à poursuivre.

État de l'art

# Applications limitées par les accès mémoire

#### Sommaire

| 1.1 Les caches                                                                          | 15        |

|-----------------------------------------------------------------------------------------|-----------|

| 1.1.1 Définition                                                                        | 15        |

| 1.1.2 La localité des accès mémoire                                                     | 16        |

| 1.1.3 Fonctionnement d'un cache                                                         | 16        |

| 1.1.4 Classification des défauts de cache                                               | 17        |

| 1.2 Caractérisation des applications                                                    | <b>17</b> |

| 1.2.1 Applications limitées par les accès mémoire                                       | 17        |

| 1.2.2 Prédictibilité des accès mémoire et prefetching                                   | 18        |

| 1.2.3 Applications limitées par la bande passante ou la latence                         | 19        |

| 1.2.4 Réutilisation et localité temporelle                                              | 19        |

| 1.3 Les principes pour concevoir une application efficace en                            |           |

| ${\rm cache}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 20        |

| 1.3.1 Les 3 principes                                                                   | 20        |

| 1.3.2 Exemple : parcourir un ensemble de points en 3 dimensions .                       | 20        |

| 1.3.3 Exemple : la multiplication de matrices                                           | 22        |

Dans ce chapitre, nous présentons le fonctionnement des caches. Nous montrons quelle est l'impact des accès mémoire sur le temps d'exécution d'une application et étudions les différentes manières de réduire cet impact. Nous montrons en particulier comment mieux utiliser les caches à travers deux principes simples que nous illustrons sur des exemples.

#### 1.1 Les caches

Nous commençons par présenter rapidement le fonctionnement des caches. On pourra consulter [HP06, Dre07] pour plus d'informations.

#### 1.1.1 Définition

Un cache est une petite zone de mémoire placée entre le processeur et la mémoire centrale (RAM) pour accélérer les accès d'un programme à ces données. La capacité du cache est plus réduite que celle de la mémoire centrale mais le temps d'accès est plus petit. En général, on retrouve plusieurs caches entre le processeur et la mémoire, avec

| Mémoire                | Capacité | Latence   | Associativité |

|------------------------|----------|-----------|---------------|

| cache de niveau 1 (L1) | 32 Ko    | 4 cycles  | 8             |

| cache de niveau 2 (L2) | 256  Ko  | 10 cycles | 8             |

| cache de niveau 3 (L3) | 8 Mo     | 40 cycles | 16            |

| RAM                    | 8 Go     | 65 cycles | NA            |

Table 1.1 – Caractéristiques des caches du processeur Intel Nehalem (Xeon 5530) [MHSM09]

une capacité et une latence croissantes. Par exemple dans le cas du processeur Intel Nehalem, il y a 3 niveaux de caches dont les capacités et latences sont reportées en table 1.1.

#### 1.1.2 La localité des accès mémoire

Les accès mémoire des programmes ont souvent certaines propriétés qui expliquent l'efficacité des caches, c'est la localité des accès mémoire. Une donnée accédée récemment a de bonnes chances d'être accédée à nouveau dans un futur proche : c'est la localité temporelle. Deux données ayant des adresses proches sont souvent accédées l'une après l'autre : c'est la localité spatiale. Ce sont ces deux propriétés qui assurent l'efficacité des caches. Si un programme ne les respecte pas, il ne bénéficiera pas de la présence de caches.

#### 1.1.3 Fonctionnement d'un cache

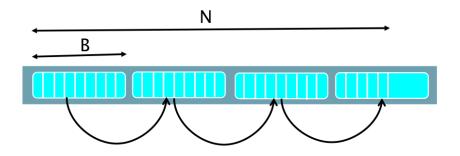

Pour réduire la latence des accès au cache grâce à la localité spatiale, les transferts entre les différents niveaux de cache et la RAM ne sont pas atomiques mais gérés par bloc de plusieurs octets : une ligne de cache. Sur le processeur Intel Nehalem, la taille des lignes de cache est de 64 octets.

Pour des raisons d'efficacité, il n'est pas toujours possible de charger une ligne à n'importe quel endroit du cache. Lorsque c'est le cas, on dit que la cache est pleinement associatif (fully associative). Si une ligne de cache ne peut être chargée qu'à une seule position, on dit que le cache est direct (direct mapped). Dans la plupart des processeurs actuels, un compromis est utilisé. Le cache est divisé en plusieurs ensembles. Chaque ensemble est pleinement associatif mais une ligne de cache ne peut être chargée que dans un seul ensemble. Ces caches sont appelés set associative. La taille d'un ensemble est l'associativité du cache.

Comme un cache a une capacité limitée, toutes les données du programme ne peuvent être chargées dans le cache au même moment. Il faut donc décider quelle ligne de cache doit être supprimée lorsqu'une nouvelle ligne doit être chargée. L'algorithme prenant cette décision est appelé algorithme de remplacement. Un algorithme très souvent utilisé est la politique LRU pour Least Recently Used. On supprime la ligne de cache dont l'accès est le moins récent. LRU étant coûteux en pratique, une approximation est utilisée dans les processeurs actuels.

Classiquement la gestion des caches est effectuée par le processeur. Toutes les données

accédées <sup>1</sup> sont placées dans le cache et le programmeur n'a pas de contrôle direct sur l'algorithme de remplacement utilisé. Dans certain cas, par exemple pour la mémoire partagée (*shared memory*) de certains GPU Nvidia, le contrôle du cache est laissé au programmeur qui peut décider quelles données seront cachées et quel algorithme de remplacement utiliser.

#### 1.1.4 Classification des défauts de cache

Lorsqu'une donnée accédée n'est pas dans le cache, elle doit y être chargée, ce qui retarde l'exécution du programme. On dit qu'accéder cette donnée cause un défaut de cache. On peut classer les défauts de cache en 3 catégories suivant le modèle 3C[HS89]. On qualifie un défaut de cache de :

Compulsory (obligatoire) si c'est le premier accès à cette donnée. Ce type de défauts de cache est inévitable car la donnée ne peut résider dans le cache.

Capacity (capacité) si on accède à une donnée chargée dans le cache précédemment mais qui n'y réside plus car elle a été expulsée par l'algorithme de remplacement. Ce type de défaut de cache peut être réduit en utilisant un cache de capacité supérieure.

Conflict (conflit) si la ligne de cache a été évincée car trop de lignes de caches sont chargées dans un même ensemble. Ce type de défaut de cache aurait pu être évité en utilisant un cache avec une associativité plus grande ou un cache pleinement associatif.

#### 1.2 Caractérisation des applications

Dans cette partie, nous montrons quel est l'impact des accès mémoire sur le temps d'exécution d'une application. Nous en déduisons des caractéristiques qui déterminent la manière d'améliorer l'application afin de réduire le temps des accès mémoire.

#### 1.2.1 Applications limitées par les accès mémoire

Pour un processeur avec un seul niveau de cache  $^2$ , on peut évaluer le temps d'exécution d'un programme  $T_{exe}$  avec la formule suivante [MPS02] :

$$T_{exe} = N \cdot [(1 - F_{memory}) \cdot T_{proc} + F_{memory} \cdot T_{memory}]$$

(1.1)

$$T_{memory} = G_{hit} \cdot T_{cache} + (1 - G_{hit}) \cdot T_{RAM} \tag{1.2}$$

avec

N le nombre d'instructions,

$T_{proc}$  le durée moyenne d'exécution d'une instruction,

$F_{memory}$  la proportion des instructions qui accèdent à la mémoire,

<sup>1.</sup> Des instructions sont disponibles dans le jeu d'instruction SSE pour spécifier qu'une donnée écrite ne doit pas être placée dans le cache.

<sup>2.</sup> Cette formule s'étend facilement au cas de plusieurs niveaux de cache.

$T_{memory}$  le temps moyen pour accéder à la mémoire,

$G_{hit}$  la proportion des accès mémoire trouvées dans le cache,

$T_{cache}$  la latence du cache et

$T_{RAM}$  la latence de la mémoire centrale.

Le premier terme de l'équation (1.1) correspond au temps passé à exécuter des calculs alors que le second terme correspond au temps passé à accéder à la mémoire. En général un processeur calcule plus rapidement qu'il n'accède à sa mémoire  $(T_{proc} \leq T_{memory})$ .

On dira qu'une application est limitée par le calcul lorsque  $F_{memory}$  est faible et donc le premier terme domine le second terme. En effet, diminuer  $T_{proc}$  en augmentant par exemple la fréquence du processeur, réduira significativement le temps d'exécution de l'application. A l'inverse une application est limitée par les accès mémoire lorsque  $F_{memory}$  est grand et donc le second terme domine le premier. Il faudra diminuer  $T_{memory}$  pour accélérer l'application. Pour cela, on peut modifier le programme pour améliorer la localité des accès mémoire ce qui rend le cache plus efficace :  $G_{hit}$  augmente. Les sections 1.3 et 2.3.1 présentent des principes et techniques pour améliorer cette localité. Une autre possibilité analysée dans les deux sous-sections suivantes est de réduire l'influence de  $T_{RAM}$  en recouvrant la latence des accès mémoire par des calculs.

Remarque. L'équation (1.1) ne s'applique pas dans le cas des processeurs out-of-order et superscalar. Cela concerne certains processeurs actuels. Dans cette configuration, le processeur peut exécuter des opérations en attendant la fin d'un accès mémoire si ces opérations sont indépendantes de l'accès mémoire. Il y a alors recouvrement entre les calculs  $T_{proc}$  et les accès mémoire  $T_{mem}$  ce qui diminue le coût apparent des accès mémoire. Cependant dans le cas des applications limitées par les accès mémoire cet effet est relativement faible.

Remarque. On peut évaluer  $F_{memory}$  en mesurant le nombre d'instructions accédant à la mémoire lors de l'exécution du programme grâce aux compteurs de performance. La bibliothèque PAPI[BDG<sup>+</sup>00] permet d'accéder facilement à ces compteurs.

#### 1.2.2 Prédictibilité des accès mémoire et prefetching

Dans la plupart des processeurs actuels, il existe un mécanisme appelé prefetching qui permet de charger dans le cache une donnée dont on aura besoin dans le futur. Le prefetching réduit la latence des accès à la mémoire centrale  $T_{RAM}$  car le transfert de la ligne de cache est lancé pendant que le processeur exécute les instructions de calculs précédant l'accès mémoire.

Le prefetching peut être réalisé automatiquement par le processeur lorsque celuici détecte un schéma d'accès mémoire régulier, par exemple un accès linéaire lors du parcours d'un tableau. Lorsque les accès mémoire ne sont pas suffisamment réguliers pour être prévus par le processeur mais sont prévisibles par le programmeur, le prefetching peut être réalisé de manière logicielle en faisant appel à certaines instructions spécialisées. Quand le prefetching matériel est possible il est préférable au prefetching logiciel car ce dernier engendre un coût en temps pour exécuter les instructions de prefetching. Quand le prefetching peut être réalisé, on dit que l'application a des accès mémoire prédictibles. Parfois, ni le processeur ni le programmeur ne peuvent prévoir l'accès mémoire suivant. Par exemple, lors du parcours d'une liste chaînée, on doit charger l'accès mémoire précédant dans le cache avant de pouvoir lancer l'accès mémoire suivant.

#### 1.2.3 Applications limitées par la bande passante ou la latence

Pour une application limitée par les accès mémoire, trois cas sont possibles après utilisation du *prefetching*.

- 1. Les accès mémoire sont prédictibles et le *prefetching* réduit très fortement  $T_{RAM}$ . L'application n'est plus limitée par les accès mémoire.

- 2. Les accès mémoire ne sont pas prédictibles et le *prefetching* est impossible. On dit que l'application est limitée par la latence.

- 3. Les accès mémoire sont prédictibles mais il n'y a pas assez de calculs pour recouvrir la latence de tous les accès mémoire. On dit que l'application est limitée par la bande passante.

Une fois que le prefetching a été considéré, si l'application est toujours limitée par ses accès mémoire (par la latence ou par la bande passante), il faut améliorer  $G_{hit}$  en augmentant la localité des accès mémoire.

Remarque. Le SMT (simultaneous multithreading ou hyperthreading) est une autre technique pour réduire l'effet de la latence des accès mémoire même dans le cas où les accès mémoire ne sont pas prédictibles. L'application doit être programmée en utilisant plusieurs threads. Lorsque l'un des threads est bloqué sur l'attente d'un accès mémoire, on exécute un autre thread. Cette technique est utilisée par les GPUs et certains processeurs.

#### 1.2.4 Réutilisation et localité temporelle

Dans une application, on définit le taux de réutilisation des données par le nombre moyen de fois où une donnée est accédée au cours de l'exécution. Faire le produit scalaire de deux vecteurs a un taux de réutilisation de 1 car chaque donnée (une composante du vecteur) n'est utilisée qu'une fois. A l'inverse, un produit  $C = A \cdot B$  de deux matrices n par n a une réutilisation de n car chaque coefficient des matrices A et B est utilisé n fois, une fois par coefficient de la matrice C sur la même ligne ou la même colonne. Lorsqu'une application a une réutilisation de 1, on ne peut pas tirer parti de la localité temporelle. S'il y a de la réutilisation, on peut évaluer la localité temporelle avec la distance de réutilisation [GST70].

On considère pour cela un espace mémoire divisé en segments de la taille d'une ligne de cache. Soit la suite  $(a_i)_{i\leq 0}$  des références à des segments mémoire d'une application. Lors de l'accès  $a_i$  à un nouveau segment  $\forall k < i, a_k \neq a_i$ , la distance de réutilisation est infinie :  $d(a_i) = +\infty$ . Lors de l'accès suivant au même segment  $a_j = a_i$  et  $\forall i < k < j, a_k \neq a_i$ , la distance de réutilisation est le nombre d'accès différents entre ces deux accès :  $d(a_j) = \text{Card}\{a_k \mid i < k < j\}$ . Dans le cas d'un cache pleinement associative géré par la politique de remplacement LRU, l'histogramme des distances de réutilisation permet d'évaluer le nombre de défauts de cache de l'application. On note

$h_d$  le nombre d'accès dont la distance de réutilisation est d. Le nombre de défaut de caches pour un cache contenant C ligne de caches est

$$Q(C) = \sum_{d=C}^{+\inf} h_d.$$

En effet, les accès ayant une distance de réutilisation infinie correspondent à des défauts de cache obligatoire (compulsory) et les accès ayant une distance de réutilisation supérieure à C sont des défauts de cache de capacité (capacity). Lors du  $C^{\text{ième}}$  accès à un nouveau segment, la ligne correspondante est évincée du cache car c'est celle dont le dernier accès est le moins récent. Ce modèle ne tient pas compte des défauts de cache de conflit (conflict) mais reste une bonne approximation [BD01] dans le cas des caches partiellement associatifs.

Améliorer la localité temporelle d'une application, revient à réduire les distances de réutilisation. Lorsque toutes les distances de réutilisation finies sont inférieures à C, le nombre de défauts de cache est minimal car les seuls défauts de cache sont les défauts de cache de type obligatoires.

# 1.3 Les principes pour concevoir une application efficace en cache

Dans cette partie, nous énonçons trois principes qu'une application doit respecter pour optimiser l'utilisation des caches. Nous illustrons ensuite notre propos par deux exemples.

#### 1.3.1 Les 3 principes

Les deux premiers principes sont à rapprocher aux propriétés de localité présentées dans la partie 1.1.2.

Localité Spatiale Une ligne de cache doit contenir autant de données utiles que possible.

Localité Temporelle Lorsqu'une donnée est dans le cache, elle doit être réutilisée le plus tôt possible.

Efficacité Appliquer les deux principes précédents doit augmenter le moins possible le nombre d'opérations.

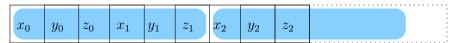

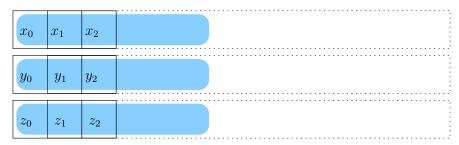

## 1.3.2 Exemple : parcourir un ensemble de points en 3 dimensions

Dans cet exemple, on travaille sur un ensemble n de points en 3 dimensions. On suppose que l'ensemble de ces points est bien plus grand que la taille du cache (n\*sizeof(double)>C). Il existe deux façons de stocker ces points en mémoire (cf. figure 1.1). La première méthode, que l'on appelle Array of Structs ou AoS, consiste à stocker les coordonnées de chaque point de manière contigüe dans une structure puis de stocker l'ensemble de ces structures linéairement en mémoire dans un tableau. La

(a) Organisation mémoire des données AoS

(b) Organisation mémoire des données SoA

```

// donnees AoS

// donnees SoA

struct mesh {

struct point {

double x[n]

double x, y, z;

double y[n]

point mesh[n];

double z[n]

// calcul par coordonnees

// calcul par coordonnees

for (int i=0; i< n; ++i)

for (int i=0; i< n; ++i)

\operatorname{mesh}[i].x = x_A ;

\operatorname{mesh.x}[i] = x_A ;

for (int i=0; i< n; ++i)

for (int i=0; i< n; ++i)

\operatorname{mesh}[i].y = y_A ;

\operatorname{mesh} . y [i] = y_A ;

for (int i=0; i< n; ++i)

for (int i=0; i< n; ++i)

\operatorname{mesh}[i].z = z_A;

\operatorname{mesh.z}[i] = z_A ;

// calcul par points

// calcul par points

for (int i=0; i< n; ++i)

for (int i=0; i< n; ++i)

\operatorname{mesh}[i].x = x_A ;

\operatorname{mesh.x}[i] = x_A ;

\operatorname{mesh}[i].y = y_A ;

\operatorname{mesh} . y [i] = y_A ;

\operatorname{mesh}[i].z = z_A ;

\operatorname{mesh.z}[i] = z_A ;

}

(d) Code pour données SoA

(c) Code pour données AoS

```

Figure 1.1 – Comparaison entre les données AoS et SoA.

deuxième méthode, Struct of Arrays ou SoA, stocke les coordonnées dans 3 tableaux différents.

Supposons que l'on réalise un changement de repère pour l'ensemble de ces points dans un repère centré au point A de coordonnées  $(x_A, y_A, z_A)$ . Il existe deux méthodes pour mettre à jour les coordonnées. On peut procéder coordonnée par coordonnée ou point par point. La façon dont on stocke les données et réalise le calcul influence fortement le nombre de défauts de cache.

Ici, les données ne sont jamais réutilisées : une coordonnée d'un point n'est utilisée qu'une fois lors de sa mise à jour. On prête donc attention à la localité spatiale. Si on réalise le calcul par coordonnées avec un stockage AoS, on ne tire pas bien parti de la localité spatiale. En effet, lors du traitement d'une coordonnée, on charge dans le cache les 3 coordonnées de chaque point car elles sont dans la même ligne de cache mais une seule est utilisée. Si on réalise le calcul par points, chaque coordonnée est utilisée immédiatement après son chargement dans le cache. Le calcul par coordonnées cause 3 fois plus de défauts de cache que le calcul par points. Dans le cas d'un stockage SoA, le calcul par coordonnées tire pleinement parti de la localité spatiale. Le calcul par points ne cause pas plus de défauts de cache si le cache peut contenir au moins 3 lignes de cache et qu'il n'y a pas de défauts de cache de conflits.

Dans tous les cas, cet exemple a des accès mémoire prédictibles par le processeur et le *prefetching* matériel rend le problème limité par la bande passante mémoire. Profiter pleinement de la localité spatiale permet de réduire le besoin en bande passante d'un facteur 3 et donc diminuer le temps d'exécution d'environ autant.

Remarque. En règle générale, on utilise le stockage AoS lorsque toutes les données de la structure sont utilisées à chaque opération sur la structure. Dans le cas inverse il vaut mieux utiliser le stockage SoA.

#### 1.3.3 Exemple : la multiplication de matrices

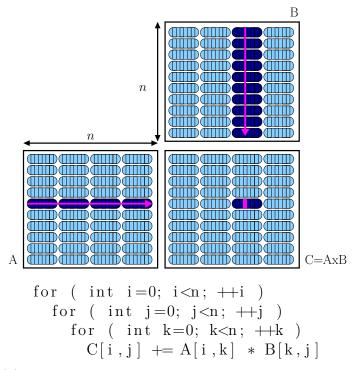

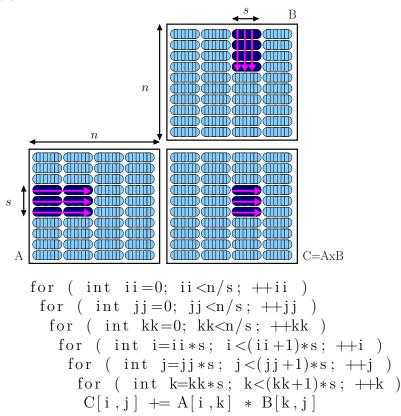

On étudie maintenant la multiplication  $C = A \times B$  de deux matrices n par n par un algorithme classique en  $O(n^3)$ . On suppose qu'une ligne de la matrice ne tient pas dans le cache.

Avec l'implémentation naïve en 3 boucles for, la localité spatiale est bonne pour les accès à la matrice A mais mauvaise pour les accès à la matrice B (cf. figure 1.2). En effet, chaque lecture d'un coefficient de B charge une ligne de cache entière contenant plusieurs coefficients mais un seul est utilisé.

La réutilisation est de n, on peut donc examiner la localité temporelle. Lors du calcul de C[i,j] on utilise la ligne A[i,:] et la colonne B[:,j]. A cause de la taille limitée du cache, la ligne A[i,:] doit être rechargée entièrement dans le cache lors du calcul de C[i,j+1]. De même pour la colonne B[:,j] lors du calcul de C[i+1,j].

Pour améliorer la localité temporelle, on peut réorganiser le calcul par blocs de taille s par s (cf. figure 1.2). On utilise un algorithme de multiplication de matrices par blocs ayant la même complexité en nombre d'opérations. Par contre, si la taille des blocs est choisie de manière à ce que 3 blocs rentrent dans le cache, c'est-à-dire  $3s^2 \leq C$ , le nombre de défauts de cache est fortement diminué. En effet, la distance de réutilisation aux lignes de A et colonnes de B est réduite ce qui améliore la localité temporelle. Lors de la multiplication de deux blocs, on peut maintenant réutiliser la partie de la

(a) Algorithme de multiplication de matrice standard

(b) Algorithme de multiplication de matrice par blocs

FIGURE 1.2 – Comparaison de deux algorithmes de multiplication de matrices. La multiplication de matrices par bloc cause moins de défauts de cache grâce à des distances de réutilisation plus faibles.

ligne A[i,:] chargée lors du calcul partiel de C[i,j] pour effectuer le calcul partiel de C[i,j+1]. De même pour les colonnes de B lors du calcul de C[i+1,j]. Cette méthode présente encore un avantage. Lors du calcul partiel de C[i,j+1], on peut utiliser la colonne de B[:,j+1] qui avait été chargée dans le cache lors du calcul de C[i,j] car elle se trouve dans les mêmes lignes de cache que la colonne B[:,j].

On analysera dans la partie 2.2.2 le nombre de défauts de cache causé par la multiplication de matrices par blocs.

# Algorithmes utilisant efficacement les caches

#### Sommaire

| 2.1 | Ana   | lyser les défauts de cache d'un algorithme 25       |

|-----|-------|-----------------------------------------------------|

|     | 2.1.1 | Le modèle cache-aware                               |

|     | 2.1.2 | Le modèle cache-oblivious                           |

|     | 2.1.3 | Limites du modèle cache-oblivious                   |

| 2.2 | Ana   | lyse de quelques algorithmes classiques             |

|     | 2.2.1 | Parcours d'un tableau                               |

|     | 2.2.2 | Multiplication de matrices                          |

|     | 2.2.3 | Recherche d'éléments dans un arbre                  |

| 2.3 | Con   | ception d'algorithmes efficaces en cache 33         |

|     | 2.3.1 | Techniques algorithmiques CA et CO                  |

|     | 2.3.2 | Performances en pratique des techniques CA et CO 35 |

| 2.4 | Algo  | orithmes CA et CO : revue des résultats 35          |

|     | 2.4.1 | Revue des algorithmes CA et CO                      |

|     | 2.4.2 | Comparaison des algorithmes CA et CO                |

Dans ce chapitre, nous donnons des techniques algorithmiques pour améliorer la localité de accès mémoires. Nous passons en revue les modèles *cache-aware* et les modèles *cache-oblivous* et montrons comment les utiliser pour analyser les défauts de cache de trois algorithmes classiques. Nous décrivons ensuite des techniques génériques pour concevoir des algorithmes efficaces dans ces modèles. Enfin, nous donnons quelques résultats théoriques et pratiques en se concentrant sur la comparaison entre les algorithmes classiques, les algorithmes *cache-aware* et les algorithmes *cache-oblivious*.

#### 2.1 Analyser les défauts de cache d'un algorithme

Concevoir des algorithmes utilisant efficacement les caches nécessite de disposer de modèles simplifiés de fonctionnement des caches. C'est grâce à ces modèles que l'on pourra analyser les performances algorithmes. Nous présentons deux de ces modèles dans les sections suivantes.

FIGURE 2.1 – Modèle cache-aware

#### 2.1.1 Le modèle cache-aware

Ce modèle porte plusieurs noms suivant les parties de la hiérarchie mémoire qu'il modélise : la mémoire centrale et le disque ou le cache et la mémoire centrale. Dans le premier cas, on parle du modèle à mémoire externe ou du modèle I/O [AV88], dans le deuxième cas, du modèle cache-aware (CA). Dans ce modèle, il y a deux niveaux de mémoire : le cache et la mémoire centrale. Les données transitent entre ces deux niveaux par blocs de taille B. Le cache a une taille M et peut donc contenir M/B blocs. L'algorithme a le contrôle du cache : lorsque le cache est plein, l'algorithme choisit quel bloc doit être évincé. De nombreux algorithmes ont été étudiés dans ce modèle. On peut consulter [Vit01]. On analysera quelques algorithmes dans la section 2.2.

#### 2.1.2 Le modèle cache-oblivious

Le modèle cache-oblivious (CO) [FLPR99] est similaire au modèle CA. On utilise le modèle CA mais on interdit à l'algorithme d'utiliser les valeurs de B et M: la taille des blocs et la taille du cache (voir figure 2.2). Le modèle CO à deux avantages majeurs par rapport au modèle CA.

Multi niveaux. Comme l'algorithme n'utilise pas la taille des blocs et du cache, les niveaux cache et mémoire centrale peuvent correspondre à n'importe quel couple de niveaux : cache  $L_1$  et cache  $L_2$ , cache  $L_2$  et cache  $L_3$ , cache  $L_3$  et mémoire centrale, etc. Un algorithme efficace dans le modèle CO est efficace sur toute la hiérarchie mémoire [FLPR99].

**Portabilité.** Comme l'algorithme n'utilise pas la taille des blocs et du cache, il est efficace quelque soient la taille des caches et des lignes de cache de la machine.

Le modèle CO comporte une autre différence avec le modèle CA. Le cache n'est plus contrôlé par l'algorithme comme dans le modèle CA mais est supposé idéal. Il est pleinement associatif et est géré par la politique de remplacement optimale : Furthest in Future (FIF). La ligne de cache évincée est celle qui sera accédée le plus tard possible. Bien sûr, cette politique de remplacement est impossible à mettre en place en pratique car elle nécessite la connaissance des accès futurs. Le papier présentant le modèle CO [FLPR99] contient des justifications théoriques pour ces deux suppositions (FIF et associativité) qu'on peut résumer ainsi : un algorithme qui cause Q(B,M) défauts de cache dans le modèle CO peut être simulé sur un cache LRU pleinement associatif avec

Figure 2.2 – Modèle cache-oblivious

O(Q(B,M)) défauts de cache si il respecte la condition de régularité suivante :

$$Q(B,M) = O(Q(B,2M)) \tag{2.1}$$

De plus un cache LRU pleinement associatif peut être implémenté dans le modèle CA sans perte de performance asymptotique.

De nombreux algorithmes ont été étudiés dans le modèle CO [ABF05]. Nous analyserons quelques algorithmes dans la section 2.2.

#### 2.1.3 Limites du modèle cache-oblivious

Le modèle CO est simple à utiliser et donne des analyses qui reflètent souvent les performances en pratique. Il comporte néanmoins quelques limites.

Le modèle CO ne prend pas en compte le prefetching. Dans certains cas, un algorithme  $A_1$  causant moins de défauts de cache qu'un algorithme  $A_2$  dans le modèle CO sera moins rapide en pratique si les accès mémoire de  $A_2$  sont prédictibles. Par exemple, l'algorithme de Floyd-Warshall qui n'est pas optimal en terme de nombre de défauts de cache est plus rapide en pratique que son équivalent optimal dans le modèle CO [PCDL07]. Il est possible d'étendre le modèle CA pour prendre en compte le prefetching [VS07] mais il n'existe pas d'approche similaire pour le modèle CO.

Le modèle CO suppose que la politique de remplacement est idéale. Dans certains cas, il y a une différence notable entre le nombre de défauts de cache en pratique et le nombre de défauts de cache prédits par le modèle CO. Par exemple, lorsqu'un algorithme mêle deux types d'accès : un accès de type *streaming* et un accès avec de la réutilisation. Dans le modèle CO, l'accès *streaming* utilisera seulement une ligne du cache laissant l'espace restant pour l'accès avec de la réutilisation. En pratique, avec une politique LRU, l'accès *streaming* utilisera beaucoup d'espace dans le cache, limitant la réutilisation pour l'autre accès.

#### 2.2 Analyse de quelques algorithmes classiques

Dans cette partie, nous analysons trois problèmes classiques dans les modèles CA et CO.

FIGURE 2.3 – Parcours d'un tableau

FIGURE 2.4 – Multiplication de matrices avec l'algorithme classique

#### 2.2.1 Parcours d'un tableau

Accéder linéairement aux données est une technique efficace dans les modèles CA et CO. On considère l'exemple du parcours d'un tableau de taille N. L'algorithme naïf est optimal car il utilise parfaitement la localité spatiale. Le nombre de défauts de cache est  $\left\lceil \frac{N}{B} \right\rceil$  (voir figure 2.3).

#### 2.2.2 Multiplication de matrices

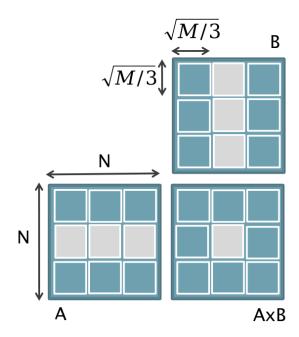

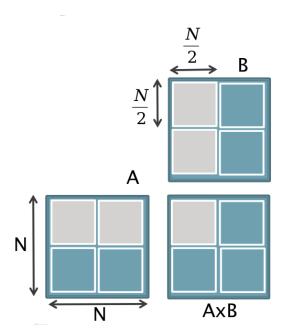

Nous avons vu dans la section 1.3.3 que l'algorithme de multiplication de matrices classique en  $O(n^3)$  cause beaucoup de défauts de cache. Nous allons évaluer ce nombre de défauts de cache dans le modèle CO et proposer deux algorithmes asymptotiquement optimaux : l'un dans le modèle CA et l'autre dans le modèle CO.

Pour des raisons de simplicité, on se limite aux cas des matrices carrés N par N. On analyse le produit  $C = A \times B$  par l'algorithme classique. Pour chaque élément C[i,j]

Figure 2.5 – Multiplication de matrices par blocs

de la matrice C, on doit charger dans le cache la ligne A[i,:] ce qui cause  $\frac{N}{B}$  défauts de cache et la colonne B[:,j] ce qui cause N défauts de cache (voir figure 2.4). Si une ligne ou une colonne est plus grande que la taille du cache, c'est-à-dire N>M, on ne peut réutiliser les données entre les calculs des éléments de la matrice C. Les accès à la matrice C sont linéaires, ils causent  $\frac{N^2}{B}$  défauts de cache. On a donc au total :

$$Q(N) = \frac{N^2}{B} + N^2 \cdot \left(\frac{N}{B} + N\right) = O(N^3)$$

défauts de cache.

On propose maintenant de calculer le produit de matrices par blocs de taille k par k, avec  $k \geq B$  (voir figure 2.5). Si 3 blocs tiennent simultanément dans le cache, c'est-à-dire  $3k^2 \leq M$ , on peut conserver à tout instant un bloc de la matrice A, un bloc de la matrice B et un bloc de la matrice C dans le cache. Multiplier deux blocs ne cause pas de défauts de cache en dehors de la lecture des blocs de A et B et de l'écriture du résultat dans C. Pour chaque bloc dans la matrice C, on doit lire  $\frac{N}{k}$  blocs dans la matrice A et dans la matrice B. La lecture d'un bloc cause  $\frac{k^2}{B}$  défauts de cache. On a donc au total :

$$\left(\frac{N}{k}\right)^2 \cdot \left(\frac{N}{k} \cdot 2 \cdot \frac{k^2}{B} + \frac{k^2}{B}\right) = O\!\left(\frac{N^3}{k \cdot B}\right)$$

On veut k le plus grand possible sachant que  $3k^2 \leq M$ . On prend donc  $k = \sqrt{\frac{M}{3}}$ , ce qui donne

$$Q(N) = O\left(\frac{N^3}{B \cdot \sqrt{M}}\right) \tag{2.2}$$

défauts de cache. Ce résultat est asymptotiquement optimal [HK81].

L'algorithme précédent a besoin de connaître la taille du cache M. Nous montrons que l'on peut atteindre la même borne sans utiliser cette valeur et obtenir ainsi un

FIGURE 2.6 – Multiplication de matrices diviser pour régner

algorithme CO. Pour cela on utilise l'algorithme de multiplication de matrices diviser pour régner. On décompose récursivement le produit en 8 produits de matrices  $\frac{N}{2}$  par  $\frac{N}{2}$ . La complexité en nombre d'instructions est

$$W(1) = O(1)$$

$$W(N) = 8W\left(\frac{N}{2}\right) + O(N^2)$$

ce qui donne  $W(N) = O(N^3)$ . On calcule de la même manière le nombre de défauts de cache. L'addition des sous-produits accède aux données linéairement et cause  $O(\frac{N^2}{B})$  défauts de cache. De plus, lorsque  $3N^2 \leq M$ , les 3 sous-matrices tiennent dans le cache donc les appels récursifs ne génèrent plus de défauts de cache. On a

$$Q(N) = 8Q\left(\frac{N}{2}\right) + O\left(\frac{N^2}{B}\right) \text{ si } 3N^2 > M$$

$$Q(N) = \frac{N^2}{B} \text{ si } 3N^3 \le M$$

ce qui donne

$$Q(N) = O\left(\frac{N^3}{B \cdot \sqrt{M}}\right) \tag{2.3}$$

Cet algorithme atteint asymptotiquement la même performance que l'algorithme précédent sans qu'il ne soit nécessaire de de connaître la taille du cache.

#### 2.2.3 Recherche d'éléments dans un arbre

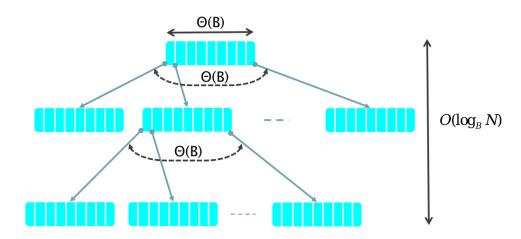

Nous considérons maintenant la recherche dans un arbre binaire équilibré contenant N éléments et de hauteur  $O(\log_2 N)$ .

FIGURE 2.7 – Recherche dans un arbre binaire

FIGURE 2.8 – Recherche d'éléments dans un B-arbre

Si on stocke chaque nœud de l'arbre séparément par exemple avec un appel à malloc, il est possible que chaque ligne de cache ne contiennent qu'un seul nœud de l'arbre (voir figure 2.7). Une autre manière classique de stocker un arbre binaire est d'utiliser un tableau T en stockant la racine dans la case T[0] et les fils gauche et droit du nœud stocké en T[i] dans les cases T[2\*i+1] et T[2\*i+2]. Dès que l'on s'éloigne de la racine, une ligne de cache ne contient que des nœuds qui ne sont pas sur le même chemin racine-feuille. On a donc besoin dans tous ces cas, d'un défaut de cache par nœud de l'arbre pour un coût total de :

$$Q(N) = h = O(\log_2 N) \tag{2.4}$$

La recherche d'éléments peut être améliorée en utilisant les B-arbres [BM72, CLRS09]. Chaque nœud de l'arbre contient  $\Theta(B)$  éléments de manière à occuper exactement une ligne de cache (voir figure 2.8). Chaque nœud est trié et a  $\Theta(B)$  fils. L'arbre est équilibré avec une hauteur  $O(\log_B N)$ . On recherche un élément en faisant une recherche binaire dans un nœud puis récursivement sur l'un des fils. La complexité est de  $W(N) = O(\log_2 B) \cdot h = O(\log_2 N)$  identique à celle de l'arbre binaire. En revanche la localité spatiale est améliorée car chaque élément d'une ligne de cache est

FIGURE 2.9 – Organisation mémoire CO d'un arbre binaire

utile. Le nombre de défauts de cache est de

$$Q(N) = 1 \cdot h = O(\log_B N) \tag{2.5}$$

soit un gain de  $O(\log_2 B)$ . Le *B*-arbre utilise la taille des lignes de cache, il est donc CA.

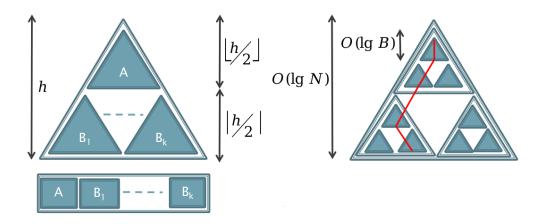

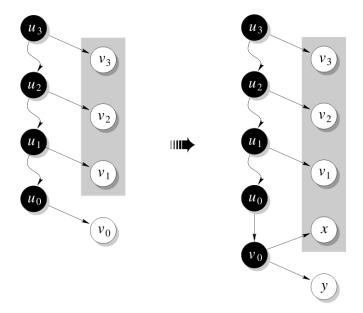

On peut obtenir des performances similaires au B-arbre dans le modèle CO en organisant avec précaution le stockage de l'arbre binaire. Pour simplifier la présentation on considère le cas d'un arbre binaire complet, pour plus de détails voir [BDFC05]. On va stocker l'arbre binaire dans un tableau T en utilisant une organisation récursive appelée van Emde Boas (voir figure 2.9). On découpe l'arbre au milieu de sa hauteur en un sous-arbre père A de hauteur  $\frac{h}{2}$  et k sous-arbres fils  $B_1, \ldots, B_k$  de hauteur  $\frac{h}{2}$ . On découpe récursivement ces sous-arbres et on les place dans le tableau dans l'ordre  $A, B_1, \ldots, B_k$ . La complexité de la recherche est identique à celle de l'arbre binaire car seule l'organisation des données en mémoire a été modifiée. Pour analyser le nombre de défauts de cache, on considère le moment où la découpe récursive a généré des sous-arbres de hauteur inférieure à  $\log_2 B$ , ainsi chaque sous-arbre tient dans une ligne de cache. Lors de la recherche d'un élément, on parcourt un chemin racine feuille qui passe successivement par

$$\frac{h}{\log_2 B} = O\left(\frac{\log_2 N}{\log_2 B}\right) = O(\log_B N)$$

sous-arbres. Or chaque sous-arbre cause un défaut de cache. On a donc au total :

$$Q(N) = O(\log_B N) \tag{2.6}$$

soit asymptotiquement le même nombre de défauts de cache que pour le B-arbre mais sans utiliser la taille des lignes de cache.

## 2.3 Conception d'algorithmes efficaces en cache

## 2.3.1 Techniques algorithmiques CA et CO

Dans cette partie, nous présentons des techniques utiles pour concevoir des algorithmes CA et CO. Ces techniques se divisent en 2 catégories :

- la réorganisation des calculs : changer l'ordre dans lesquels les calculs sont effectués

- la réorganisation des données : changer la façon dont les données sont organisées en mémoire.

#### Accès séquentiel aux données

L'accès séquentiel est une manière très efficace d'accéder aux données car il permet une utilisation optimale de la localité spatiale. Cette technique ne nécessite pas la connaissance des tailles de cache ni de ligne de cache, on peut donc l'utiliser dans les deux modèles CA et CO. Elle est analysée dans la section 2.2.1.

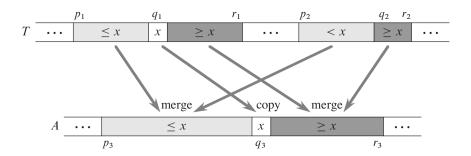

#### Trier les données

Il existe plusieurs algorithmes de tri CA et CO efficaces en cache. On peut évidemment les utiliser pour remplacer leurs alternatives classiques (tri fusion ou tri rapide) si l'algorithme à rendre efficace comporte une étape de tri. On peut également utiliser un tri CA ou CO pour rendre efficace en cache un algorithme qui ne comportait pas d'étape de tri. Cette technique permet d'améliorer une étape comportant beaucoup d'accès mémoire aléatoires qui sont mauvais pour la localité. Par exemple dans le cas des algorithmes sur les graphes, on visite souvent l'ensemble des nœuds en utilisant les informations de connectivité ce qui génère des accès aléatoires aux nœuds. Si on peut obtenir efficacement l'ordre dans lequel on doit visiter les nœuds du graphe, on peut trier les nœuds dans cet ordre puis utiliser des accès séquentiels.

#### Calcul par blocs

La technique de calcul par blocs consiste à partitionner l'ensemble des opérations à effectuer en blocs, chaque bloc accédant à un même sous-ensemble des données. Cette technique permet notamment d'augmenter la localité temporelle en réduisant les distances de réutilisation. Cette technique est en général utilisée pour des algorithmes CA car on choisit la taille des blocs de manière à ce que la quantité de données accédées par un bloc soit inférieure à la taille du cache. Un exemple d'utilisation de cette technique est la multiplication de matrices par blocs présentée dans la section 2.2.2.

#### Diviser pour régner

Les algorithmes de type diviser pour régner sont une alternative CO à la technique CA du calcul par blocs. L'ensemble des calculs à effectuer est divisé récursivement en blocs de plus en plus petits. Il existe donc un niveau de la découpe récursive dans lequel les blocs sont plus petits que la taille du cache. Ainsi il n'est pas nécessaire de connaître la taille du cache pour utiliser cette technique. C'est la méthode utilisée par l'algorithme de multiplication de matrices CO de la section 2.2.2.

#### Organisation mémoire par blocs

L'organisation mémoire par blocs est analogue à la technique de calcul par blocs mais pour les données. On découpe la structure de données de manière à ce qu'une sous-partie contigüe des calculs accède à un même bloc de données. Cela permet entre autres d'augmenter la localité spatiale. Cette technique est plutôt utilisée dans les algorithmes CA car on choisit en général la taille des blocs en fonction de la taille des lignes de cache. Un exemple d'utilisation de cette méthode est le B-arbre présenté dans la section 2.2.3.

#### Organisation mémoire récursive

L'organisation mémoire récursive est l'alternative CO de l'organisation mémoire par blocs. Les données sont découpées récursivement en morceaux de plus en plus petits. Il existe un niveau de la découpe récursive dans lequel les blocs sont plus petits que la taille d'une ligne de cache. Il n'est donc pas nécessaire de connaître la taille des lignes de cache. C'est la méthode utilisée par le B-arbre CO de la section 2.2.3.

#### Space Filling Curves

L'utilisation des space filling curves est un cas particulier des techniques diviser pour régner pour les calculs et d'organisation mémoire récursive pour les données. On considère des découpes en blocs récursives spécifiques qui correspondent à des space filling curves comme par exemple la courbe de Lebesgue ou la courbe de Hilbert. En utilisant ces courbes, on peut parcourir ou stocker de manière locale des données multidimensionnelles. Ces courbes fournissent une meilleure localité qu'une découpe récursive classique. De plus il est possible de les utiliser de manière itérative ce qui peut améliorer les performances. Ces courbes ont été utilisées par exemple pour construire des algorithmes CO de multiplication de matrices [BZ05] ou des organisations mémoire de maillages réguliers [PF01].

#### Partitionnement ou regroupement

Ces techniques sont analogues à l'organisation mémoire par blocs pour les structures de données irrégulières à base de pointeurs. Par exemple les structures de données utilisées pour les matrices creuses, les graphes, les maillages. Contrairement au cas régulier où on doit généralement changer le code du calcul si on réorganise les données, ce n'est pas nécessaire pour le cas irrégulier. En effet, comme le code du calcul suit des pointeurs, il suffit de changer leur destination pour changer l'organisation des données. Le partitionnement et le regroupement ont pour but de stocker de manière contigüe les données qui sont accédées consécutivement par le calcul. On peut soit regrouper en mémoire des données utilisées en même temps par le calcul, soit partitionner les données en sous-ensembles qui sont utilisés à différents moments du calcul. Pour cela on utilise souvent des techniques de partitionnement de graphes avec une connectivité déduite de l'utilisation des données dans l'algorithme. Si on cherche à obtenir des partitions de taille fixée on obtient une méthode CA. L'utilisation de cette technique de manière récursive (hiérarchique) permet d'obtenir une méthode CO.

#### Duplication de données